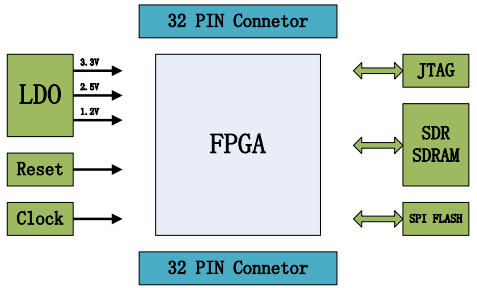

SF-CY3 ║╦ą─░Õ│²┴╦ę╗Ņw░║┘FĄ─ FPGA ąŠŲ¼═ŌŻ¼ļŖį┤ĪóÅ═╬╗ĪóĢrńŖĪóJTAG ę╗éĆ▓╗─▄╔┘ĪŻ

╬ęéā▀@┐╔ŅwąŠŲ¼Ą─ļŖį┤ėą╚²ÖnŻ¼╝┤3.3VĪó2.5V║═1.2VĪŻ3.3V╩Ū╣®Įo FPGA Ą─I/O ļŖē║Ż¼ę▓╩ŪŽĄĮyĄ─Ųõ╦¹═ŌįOąŠŲ¼Ż©╚ńSDR SDRAM║═SPI FLASHŻ®Ą─ļŖį┤ļŖē║Ż╗2.5V╩Ū╣®Įo JTAGļŖ┬Ę║═FPGA Ą─PLL ļŖį┤╦∙ąĶꬥ─Ż╗1.2Vät╩Ū FPGA Ą─ā╚║╦ļŖē║ĪŻ╩╣ė├Ą─ĢrńŖ╩Ū 25MHzŻ¼ėą╚╦šf▀@├┤Ą═Ż¼▓╗ē“ė├Ą─Ż┐ĘŪę▓Ż¼FPGA ā╚▓┐Ą─ PLL Š═╩ŪīŻķTžōž¤╣▄└ĒĢrńŖĄ─Ż¼╦³┐╔ęįī”═Ō▓┐▌ö╚ļĄ─ 25MHzĢrńŖ▒ČŅl╗“ĘųŅlŻ¼╔§ų┴ĘŪš¹öĄ▒ČĄ─▒ČŅl╗“ĘųŅlę▓─▄ē“▐kĄĮĪŻJTAG ╩Ūė├ė┌PC║═FPGA ▀BĮėĄ─ļŖ┬ĘŻ¼PC╔ŽĄ─Quartus IIŽ┬▌d¤²õøŠ═╩Ū═©▀^▀@éĆĮė┐┌ĪŻ

į┌▀^╚źŻ¼║Ō┴┐ę╗éĆ▀ē▌ŗŲ„╝■Ą─┘Yį┤ŪķørŻ¼āHāH┐┤╦¹Ą─▀ē▌ŗ┘Yį┤▒Ń┐╔ų¬Ųõę╗Č■Ż¼Ą½ļSų°ųŲįņ╣ż╦ćĄ─▓╗öÓ▀M▓ĮŻ¼┤¾┴┐Ą─┤µā”Ų„Īó│╦Ę©Ų„┘Yį┤┐╔ęį║▄▌pęūĄ─Øō╚ļĄĮ┐╔ŠÄ│╠▀ē▌ŗŲ„╝■ų«ųąŻ¼┤¾┤¾▒Ń└¹įOė├æ¶Ą─įOėŗĪŻ

╦∙ęįŻ¼Į±╠ņ╬ęéā▒žĒÜ═¼Ģr╚ź║Ō┴┐▀@ą®▀ē▌ŗŲ„╝■ųą╦∙░³║¼Ą─┤µā”Ų„Īó│╦Ę©Ų„╔§ų┴ĢrńŖĪóI/O Ą─┘Yį┤ŪķørŻ¼«ģŠ╣╦¹éāę▓║═╬ęéāĄ─īŹļHæ¬ė├ŽóŽóŽÓĻPĪŻCyclone IIIŲ„╝■▓╔ė├┴╦│╔╩ņĄ─ 65ns ╣ż╦ćŻ¼│²┴╦ōĒėąžSĖ╗Ą─▀ē▌ŗ┘Yį┤═ŌŻ¼┤µā”Ų„┘Yį┤Īó│╦Ę©Ų„┘Yį┤ĪóĢrńŖ┘Yį┤ĪóI/O ┘Yį┤ę▓ĘŪ│ŻžSĖ╗Ż¼┐╔ęįØMūŃ┤¾ČÓöĄĄ─ųąĄ╚ęÄ─ŻęįŽ┬Ą─æ¬ė├ĪŻÅ─ handbookųąĮžŽ┬ę╗éĆ┘Yį┤Ęų▓╝▒ĒŻ¼Å─▀@└’╬ęéā▒Ń┐╔ī” Cyclone III╝ęūÕĖ„éĆą═╠¢Ų„╝■Ą─┘Yį┤Ūķørę╗─┐┴╦╚╗ĪŻ

- PC╣┘ĘĮ░µ

- ░▓ū┐╣┘ĘĮ╩ųÖC░µ

- IOS╣┘ĘĮ╩ųÖC░µ

DJI ┤¾Į«’wąą─ŻöM1.4╣┘ĘĮ░µ

DJI ┤¾Į«’wąą─ŻöM1.4╣┘ĘĮ░µ

┬ōŽļę╗µIĮ¹ų╣“īäėĖ³ą┬╣żŠ▀2.26.1 ųą╬─ŠG╔½░µ

┬ōŽļę╗µIĮ¹ų╣“īäėĖ³ą┬╣żŠ▀2.26.1 ųą╬─ŠG╔½░µ

ĻPķ]ė▓▒P║ąūįäėą▌├▀▄ø╝■ĖĮĮ╠│╠

ĻPķ]ė▓▒P║ąūįäėą▌├▀▄ø╝■ĖĮĮ╠│╠

ELM327“īäė1.0 ╣┘ĘĮ░µ

ELM327“īäė1.0 ╣┘ĘĮ░µ

PowerPCBļŖ┬ĘįOėŗīŹė├Į╠│╠pdfļŖūė░µ

PowerPCBļŖ┬ĘįOėŗīŹė├Į╠│╠pdfļŖūė░µ

PowerPCBĖ▀╦┘ļŖūėļŖ┬ĘįOėŗ┼cæ¬ė├pdfĖ▀ŪÕļŖūė░µ

PowerPCBĖ▀╦┘ļŖūėļŖ┬ĘįOėŗ┼cæ¬ė├pdfĖ▀ŪÕļŖūė░µ

ļŖ┬Ę╝░ļŖ╣ż╝╝ąg╗∙ĄApdfĖ▀ŪÕļŖūė░µ

ļŖ┬Ę╝░ļŖ╣ż╝╝ąg╗∙ĄApdfĖ▀ŪÕļŖūė░µ

ė▓▒Pē─Ą└ą▐Å═Į╠│╠doc ├Ō┘M░µ

ė▓▒Pē─Ą└ą▐Å═Į╠│╠doc ├Ō┘M░µ

Revit MEP╚ļķTĮ╠│╠╣┘ĘĮ░µdoc ūŅą┬░µ

Revit MEP╚ļķTĮ╠│╠╣┘ĘĮ░µdoc ūŅą┬░µ

ą┬ŠÄļŖ─XĮMčb┼cė▓╝■ŠSą▐Å─╚ļķTĄĮŠ½═©pdf Ė▀ŪÕ├Ō┘M░µ

ą┬ŠÄļŖ─XĮMčb┼cė▓╝■ŠSą▐Å─╚ļķTĄĮŠ½═©pdf Ė▀ŪÕ├Ō┘M░µ

ė▓╝■ŽĄĮy╣ż│╠ĤīÜĄõpdf├Ō┘MļŖūė░µ

ė▓╝■ŽĄĮy╣ż│╠ĤīÜĄõpdf├Ō┘MļŖūė░µ

xbox one╩ų▒·▀BĮėļŖ─XĮ╠│╠doc═Ļš¹├Ō┘M░µ

xbox one╩ų▒·▀BĮėļŖ─XĮ╠│╠doc═Ļš¹├Ō┘M░µ

ė▓╝■╣ż│╠Ĥ╚ļķTĮ╠│╠pdfĖ▀ŪÕ├Ō┘MŽ┬▌d

ė▓╝■╣ż│╠Ĥ╚ļķTĮ╠│╠pdfĖ▀ŪÕ├Ō┘MŽ┬▌d

Hyper-v╠ōöMÖC╚ń║╬įLå¢USBįOéõdoc═Ļš¹░µ

Hyper-v╠ōöMÖC╚ń║╬įLå¢USBįOéõdoc═Ļš¹░µ

ļŖ─Xų„░Õ╠°ŠĆĄ─ĮėĘ©įöĮŌdocūŅą┬├Ō┘M░µ

ļŖ─Xų„░Õ╠°ŠĆĄ─ĮėĘ©įöĮŌdocūŅą┬├Ō┘M░µ

ŠĆąįĘĆē║Ų„╗∙ĄAų¬ūRpdf═Ļš¹░µ

ŠĆąįĘĆē║Ų„╗∙ĄAų¬ūRpdf═Ļš¹░µ

ModelSim║å├„╩╣ė├Į╠│╠pdf░µ

ModelSim║å├„╩╣ė├Į╠│╠pdf░µ

öĄūųļŖūė╝╝ąg╗∙ĄAĮ╠│╠(ķÉ╩»Ą┌5░µ)pdf░µ

öĄūųļŖūė╝╝ąg╗∙ĄAĮ╠│╠(ķÉ╩»Ą┌5░µ)pdf░µ

ļŖ┬ĘĄ┌╬Õ░µŪ±ĻPį┤pdfĖ▀ŪÕ├Ō┘M░µ

ļŖ┬ĘĄ┌╬Õ░µŪ±ĻPį┤pdfĖ▀ŪÕ├Ō┘M░µ

ėŗ╦ŃÖCĮM│╔┼cįOėŗė▓╝■▄ø╝■Įė┐┌Ą┌╬Õ░µpdfĖĮ┤░Ė═Ļš¹░µ

ėŗ╦ŃÖCĮM│╔┼cįOėŗė▓╝■▄ø╝■Įė┐┌Ą┌╬Õ░µpdfĖĮ┤░Ė═Ļš¹░µ

Į╚┌¤ÆĮąg(įŁ░µ)pdfĖ±╩ĮĪŠųą╬─═Ļš¹░µĪ┐

Į╚┌¤ÆĮąg(įŁ░µ)pdfĖ±╩ĮĪŠųą╬─═Ļš¹░µĪ┐

╔Ņ╚ļPHP├µŽ“ī”Ž¾─Ż╩Į┼cīŹ█`(ųą╬─Ą┌╚²░µ)pdfĖ▀ŪÕÆ▀├Ķ░µĪŠ═Ļš¹░µĪ┐

╔Ņ╚ļPHP├µŽ“ī”Ž¾─Ż╩Į┼cīŹ█`(ųą╬─Ą┌╚²░µ)pdfĖ▀ŪÕÆ▀├Ķ░µĪŠ═Ļš¹░µĪ┐

HADOOPīŹæ(ųą╬─Ą┌Č■░µ)pdfŪÕ╬·═Ļš¹ļŖūė░µ

HADOOPīŹæ(ųą╬─Ą┌Č■░µ)pdfŪÕ╬·═Ļš¹ļŖūė░µ

┤¾öĄō■Ģr┤· ╔·╗Ņ╣żū„┼c╦╝ŠSĄ─┤¾ūāĖ’pdfųą╬─═Ļš¹░µ├Ō┘MŽ┬▌d

┤¾öĄō■Ģr┤· ╔·╗Ņ╣żū„┼c╦╝ŠSĄ─┤¾ūāĖ’pdfųą╬─═Ļš¹░µ├Ō┘MŽ┬▌d

U▒PčbŽĄĮy(ā×▒P░▓čb▓┘ū„ŽĄĮy)łDĮŌĮ╠│╠ PDFpdf═Ļš¹Ė▀ŪÕ░µĪŠĖĮį┤┤·┤aĪ┐├Ō┘MŽ┬▌d

U▒PčbŽĄĮy(ā×▒P░▓čb▓┘ū„ŽĄĮy)łDĮŌĮ╠│╠ PDFpdf═Ļš¹Ė▀ŪÕ░µĪŠĖĮį┤┤·┤aĪ┐├Ō┘MŽ┬▌d

ÖCąĄįOėŗ╩ųāįĄ┌╬Õ░µļŖūė░µpdfĖ▀ŪÕ├Ō┘M░µ

ÖCąĄįOėŗ╩ųāįĄ┌╬Õ░µļŖūė░µpdfĖ▀ŪÕ├Ō┘M░µ

ūC╚»Ęų╬÷Ą┌┴∙░µpdfĖ±╩ĮĖ▀ŪÕ├Ō┘M░µĪŠ═Ļš¹░µĪ┐

ūC╚»Ęų╬÷Ą┌┴∙░µpdfĖ±╩ĮĖ▀ŪÕ├Ō┘M░µĪŠ═Ļš¹░µĪ┐

»é┐±javaųv┴x(Ą┌3░µ)pdf (ųą╬─░µ)ļŖūė░µ

»é┐±javaųv┴x(Ą┌3░µ)pdf (ųą╬─░µ)ļŖūė░µ

├„│»─Ūą®╩┬ā║¤oäh£ptxt╚½╝»Ž┬▌d

├„│»─Ūą®╩┬ā║¤oäh£ptxt╚½╝»Ž┬▌d JGJ145-2013╗ņ─²═┴ĮYśŗ║¾Õ^╣╠╝╝ągęÄ│╠pdf═Ļ

JGJ145-2013╗ņ─²═┴ĮYśŗ║¾Õ^╣╠╝╝ągęÄ│╠pdf═Ļ ╣½┬ĘBūo░▓╚½ū„śIęÄ│╠JTG H30Ī¬2015pdfĖ▀ŪÕ

╣½┬ĘBūo░▓╚½ū„śIęÄ│╠JTG H30Ī¬2015pdfĖ▀ŪÕ šn│╠▒Ē┐š░ū▒ĒĖ±ĪŠ├Ō┘MŽ┬▌d░µĪ┐

šn│╠▒Ē┐š░ū▒ĒĖ±ĪŠ├Ō┘MŽ┬▌d░µĪ┐ čb┼õ╩Į╗ņ─²═┴ĮYśŗ╝╝ągęÄ│╠JGJ1-2014pdfļŖūė

čb┼õ╩Į╗ņ─²═┴ĮYśŗ╝╝ągęÄ│╠JGJ1-2014pdfļŖūė ╗ņ─²═┴ÅŖČ╚Öz“×įuČ©ś╦£╩GB/T50107-2010ļŖūė

╗ņ─²═┴ÅŖČ╚Öz“×įuČ©ś╦£╩GB/T50107-2010ļŖūė ś╦£╩ęĢ┴”▒ĒĖ▀ŪÕ┤¾łD(A4┤“ėĪ░µęĢ┴”▒Ē)bmpĖ±╩Į

ś╦£╩ęĢ┴”▒ĒĖ▀ŪÕ┤¾łD(A4┤“ėĪ░µęĢ┴”▒Ē)bmpĖ±╩Į Ųš═©╗ņ─²═┴┼õ║Ž▒╚įOėŗęÄ│╠JGJ/55-2011pdfļŖ

Ųš═©╗ņ─²═┴┼õ║Ž▒╚įOėŗęÄ│╠JGJ/55-2011pdfļŖ ¤ßĮ╗ōQŲ„GB/T151-2014pdfļŖūė═Ļš¹Ė▀ŪÕ░µ├Ō┘M

¤ßĮ╗ōQŲ„GB/T151-2014pdfļŖūė═Ļš¹Ė▀ŪÕ░µ├Ō┘M õōĮŅ║ĖĮė╝░“×╩šęÄ│╠JGJ18-2012pdfÆ▀├ĶĖ▀ŪÕ░µ

õōĮŅ║ĖĮė╝░“×╩šęÄ│╠JGJ18-2012pdfÆ▀├ĶĖ▀ŪÕ░µ